- 回首頁

- 機械工業雜誌

電漿摻雜活化之微波退火技術

作者 黃昆平、季耀仁

刊登日期:2019/06/01

摘要:隨著半導體技術演進,對鰭式電晶體淺接面摻雜及活化困難到越來越高。鰭式電晶體的鰭越做越高,且間距越做越小,傳統離子佈植及雷射活化已無法滿足需求。為避免離子佈植破壞矽晶格或因寬深比(aspect ratio)的因素造成摻雜不完全之缺點,利用化學沉積法之電漿摻雜,可彌補離子佈植之缺點;另外,寬深比大之鰭式電晶體之鰭片底部的摻雜活化,由於傳統光學加熱如快速升溫退火(rapid thermal annealing, RTA)或雷射(Laser)之高溫退火,一則容易造成淺接面的摻雜擴散,二則由於光學穿透不佳,無法對鰭片底部摻雜之活化。此外,本文亦將首次介紹多片晶圓微波退火的優異成果。

Abstract:With the evolution of semiconductor technology, it is difficult to dope and activate shallow junction of FinFET transistors. The height of fins of FinFET transistors are getting greater and the spacing between fins is getting smaller. As such, the traditional ion implantation and laser activation cannot meet the demand. In order to avoid the defects of ion implantation caused by the destruction of the silicon lattice or the incomplete doping due to the high aspect ratio, the plasma doping by the chemical vapor deposition method can compensate for the shortcomings of the ion implantation. The doping activation at the fin bottom of the high aspect ratio transistor is due to the high temperature annealing of the conventional optical heating such as rapid thermal annealing (RTA) or laser, the former of which tends to cause the doping diffusion of the shallow junction, and the latest of which is due to the poor optical penetration. In addition, this paper will introduce the excellent results of multi-wafer microwave annealing for the first time.

關鍵詞:微波、半導體、電漿摻雜

Keywords:Microwave, Semiconductor, Plasma doping

前言

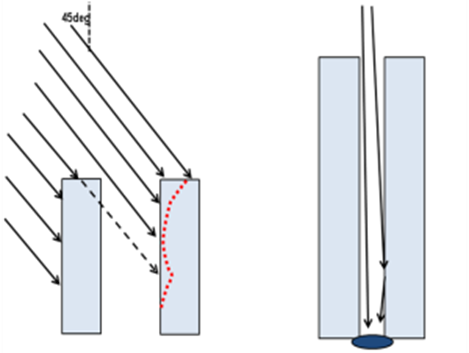

隨著半導體技術發展,傳統離子佈植在五奈米以下線寬的淺接面摻雜的挑戰越來越高,特別是鰭式電晶體因為摻雜角度關係遮蔽,鰭片容易造成遮蔽及穿透效應,直接影響離子佈植的均勻性[1,2]如圖1所示;此外,隨著閘極線寬越做越窄,鰭片間距越作越窄,而鰭片也越作越高,傳統離子佈植法應用上明顯受到幾何上的限制,以及摻雜活化均勻性亦同樣受到結構上的幾何限制。

(a) (b) (c)

圖1 (a)離子佈植製程中因摻雜角度對鰭片的遮蔽及穿透效應,造成摻雜的不均勻性(b)鰭片的高寬深比,造成底部摻雜濃度過低[1](c)離子佈植因能量關係摻雜元素造成表面矽原子晶格排列的破壞[2]

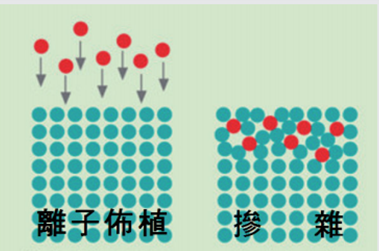

在未來半導體的應用上為解決離子佈植的缺點,對矽晶格損害較小電漿摻雜逐步受到重視。電漿浸沒離子佈植(plasma immersion ion implantation)或電漿摻雜(plasma doping)法,傳統上可利用高密度電漿進行雜質摻雜例如中空陰極(HC)[3]、電子迴旋共振(ECR)[4]或電感耦合(ICP)[5]電漿等,利用其低能量離子作為摻雜之電漿源,進行超淺接面(ultra-shallow junction)高劑量之摻雜。

本研究使用IBS公司出品之Pulsion Nano設備如圖2所示,其是屬於ICP高密度電漿設備,可對12吋以下矽晶圓控片進行p-type (BF3)及n-type (AsH3)之離子摻雜,摻雜能量及濃度分別為3.3keV/1E16 cm-3及8keV/1E16 cm-3,並用自行開發之多重模態微波退火設備[6]對摻雜物質進行活化,以期達到低溫摻雜活化且摻雜物質無擴散之目的,研究並比較與RTA及雷射退火之差異。

圖2 研究使用之IBS公司出品之Pulsion Nano電漿摻雜設備的腔體示意圖

多重模態微波退火

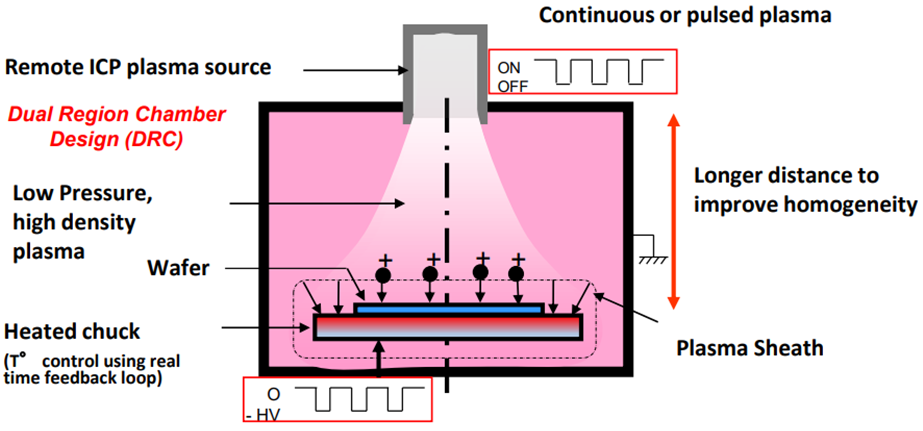

微波退火基本上由於矽晶格會直接震盪吸收,可做到低溫活化摻質,再者微波可穿透奈米金屬而無圖案效應的問題,可避免退火不均勻性的問題,如此可做到低溫摻質活化符合半導體製程未來的需求。由於矽晶格對微波共振吸收頻率為2.7 GHz,而矽與砷或矽與二氟化硼對微波的共振吸收頻率分別3.8及3.9 GHz。實際上這三個共振吸收頻率與工業用之2.45 GHz磁控管輸出頻率較為接近,故研究採用2.45 GHz磁控管作為微波源;然而微波模態數與頻率平方成正比,為彌補低頻微波模態數少的缺點,研究使用(1)空間模態分岐技術及(2)時間相位交錯技術一舉增加四倍數模態數,達到比5.8 GHz磁控管產生更多之模態數目[7]。

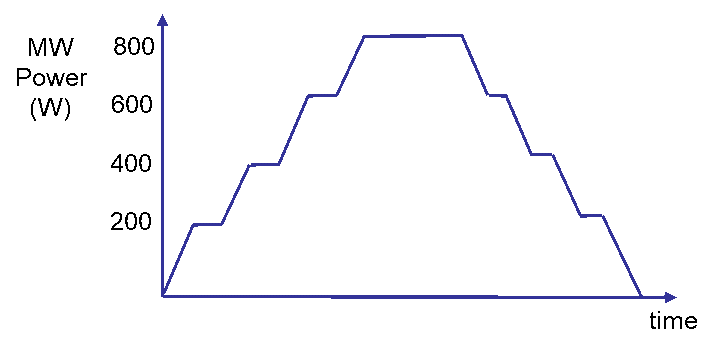

為誘使微波對矽晶圓的吸收效果,可利用高介電常數材料作為襯片(susceptor wafers)有效侷限微波,使矽晶片有效吸收微波恢復單晶晶格並活化摻雜元素。然而,這些高介電常數材料諸如石英、碳化矽、純矽、或氧化鋁等等,均屬脆性的離子鍵或共價鍵材料,很容易在快速升降溫的退火過程中脆裂;此外,供半導體使用之襯片通常要求為高純度,在製作上成本甚至比矽晶片還要高出許多;因此,為延長襯片的使用壽命,必須將微波加熱設備之所有磁控管做分段加熱或降溫,由於不像一般加熱設備可藉熱電耦溫度計回溯控制,直接利用磁控管陽極電流回溯控制輸出瓦數,如圖3所示,如此可避免高介電脆性材料在劇烈的升降溫的操作環境下破裂。研究使用比較介電常數ε=6.6之SiC及ε=9.9之Al2O3兩種材料作為砷離子佈植12吋晶圓微波退火的襯片,進行微波退火實驗,其成效由圖4得知介電常數較高的Al2O3襯片可獲得較低的片電阻值(較高的活化率)及較低的不均勻性,特別是在不均勻性方面可做到小於1%,可輔助微波退火達到半導體摻雜活化的標準。

圖3 顯示利用微波陽極電流回溯控制磁控管功率輸出

回文章內容列表更完整的內容歡迎訂購 2019年06月號 (單篇費用:參考材化所定價)

主推方案

無限下載/年 5000元

NT$5,000元

訂閱送出