- 回首頁

- 機械工業雜誌

- 歷史雜誌

電漿離子能量分佈量測技術

作者 張家豪、蘇郁仁、黃威

刊登日期:2022/10/01

摘要:現代半導體元件製造過程中,舉凡電漿蝕刻(plasma etch)、電漿輔助化學氣相沉積(PECVD)、物理氣相沉積(PVD)等電漿相關製程均扮演極為重要的角色。如何提升製程良率及產量,成為製造商彼此間相互競爭的重點開發項目,也是設備廠商所需面對的課題之一。而隨著半導體元件尺寸不斷縮小,使用材料多元化,對於製程技術與設備開發所面臨的挑戰也就更加嚴苛,唯有深入了解製程腔體中電漿特性參數,才能夠掌握製程反應機制與結果。而電漿蝕刻製程中離子能量大小對製程結果,諸如蝕刻率、蝕刻選擇比及表面輪廓控制等,都有顯著的影響。本文將針對離子能量分佈(Ion Energy Distribution, IED)量測方法進行介紹。

Abstract:In modern semiconductor device manufacturing industry, the plasma processing plays a crucial role in processes such as dry etching, plasma-enhanced chemical vapor deposition (PECVD) and physical vapor deposition (PVD), etc.; whereas high yield and high throughput are of primary important challenge for the semiconductor manufacturers to breakthrough and to enhance competitiveness. As the semiconductor device sizes decrease to nanoscale and new semiconductor materials emerge, it is more difficult to develop an advanced manufacturing process and equipment. It is desirable to diagnose the plasma properties to understand plasma mechanism in depth, in order to improve process stability and reliability. In a plasma processing, the energy of bombarding ions critically controls the surface reactions. Especially in etching process, the ion energy is typically controlled coarsely with a sinusoidal bias voltage applied to the substrate electrode, producing a broad bimodal ion energy distribution (IED), which influences the etch rate, selectivity and surface profile, etc. In this article, an ion energy distribution diagnostic technology will be introduced.

關鍵詞:電漿量測、離子能量分佈、柵極式離子能量分析儀

Keywords:Plasma diagnostic, Ion energy distribution, Gridded ion energy analyzer

前言

電漿蝕刻製程是半導體元件圖案轉移的重要關鍵技術,諸如淺溝槽絕緣(Shallow Trench Isolation, STI)、閘極氧化層(gate oxide)、金屬導線、導通孔(via hole)等,都需要精準蝕刻控制以完美轉移IC設計圖案到矽晶圓上。電漿蝕刻有化學性、物理性以及離子輔助等三種蝕刻機制存在[1-2],其中,化學性蝕刻是由電漿所產生的中性蝕刻反應物種與待蝕刻表面直接反應生成揮發性蝕刻副產物(byproduct),若副產物不具揮發性就無法被真空抽氣帶走以進行下一次蝕刻反應,此類型蝕刻機制最大特點是等向蝕刻特性(isotropic etching)及優異的蝕刻選擇特性; 而物理性蝕刻是利用離子轟擊基板,藉由動能轉移將表面原子敲擊濺射出來(sputtering),由於離子運動與所施加的電場方向有關,因此具備非等向性蝕刻特性(anisotropic etching),且蝕刻速率/濺射產率(sputtering yield)與離子速度(轟擊能量開根號)成正比[3],然而只要離子轟擊能量超越基板材料臨界濺射能量(threshold energy),即會產生濺射反應,因此蝕刻選擇性並非此類型設備(PVD)討論重點; 離子輔助蝕刻則是綜合化學性與物理性兩種機制同時存在,首先是電漿中蝕刻反應物與待蝕刻表面原子產生吸附反應(adsorption reaction),接著是帶能量離子轟擊基板藉由能量轉移使得表面蝕刻產物由固態轉成氣態揮發或濺射掉。以高密度氯氣電漿蝕刻多晶矽為例,首先是電漿中氯分子受電子碰撞反應產生氯原子、電子及氯離子等各種粒子,其中氯原子與多晶矽吸附鍵結為SiCl(s)、SiCl2(s)、SiCl3(s)等固態化合物,之後氯離子(Cl+、Cl2+)轟擊這些化合物使其氣化後被真空系統抽走,完成蝕刻反應流程。而在相同的氯原子對氯離子的通量比值狀況下,離子輔助蝕刻的蝕刻速率是物理性蝕刻的數百倍、化學性蝕刻的數百至數千倍。也因為蝕刻過程離子扮演如此重要之角色,對於要了解蝕刻製程結果背後之物理及化學機制或是優化提升蝕刻設備性能,極需要對離子能量特性進行探討。

蝕刻離子能量分佈

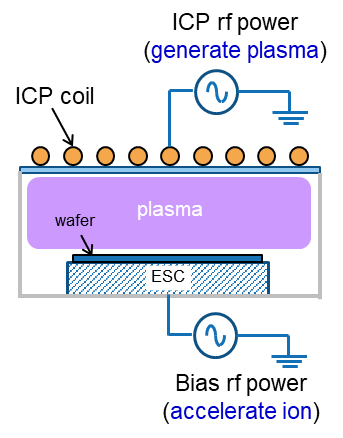

電漿蝕刻利用射頻偏壓來吸引離子產生能量,如圖1所示。當於承載晶圓的電極板上(一般為Electrostatic Chuck, ESC)施予射頻功率時,考慮電漿維持電中性的特性,在一個射頻週期時間內,到達晶圓表面帶電粒子之正負電荷總數會維持相同(正電荷離子數量等於負電荷電子數量),而由於電漿中離子質量遠大於電子質量,其速度遠小於電子速度,因此吸引正離子到達晶圓表面之負半波週期時間需要長一些,而吸引負電荷電子的正半波週期時間則少許多,如圖2所示,在平衡狀態下,單位射頻週期時間內,到達基板之電荷淨值總合須維持為零,也就是對時間積分所得之電子數量等於正離子數量,進而造成所施加的射頻功率電壓其位準會向下(負)偏移,此現象稱之為射頻自我偏壓(rf self-bias)[2, 4]。從巨觀尺度觀察,對時間平均而言,正電荷離子在通過電漿鞘層到達晶圓表面過程中,會受此負偏壓吸引而加速產生能量以轟擊晶圓進行蝕刻反應[3-5]。

圖1 ICP蝕刻電漿源示意圖,其中ICP射頻功率用以產生電漿,偏壓射頻功率則用以吸引離子轟擊晶圓表面

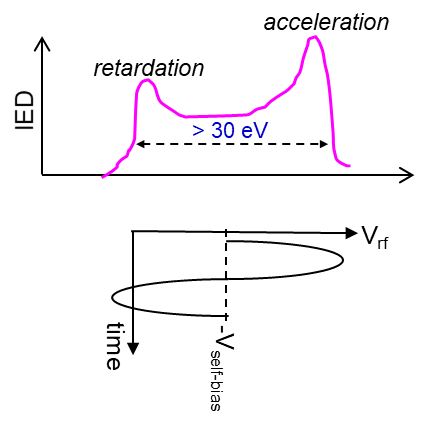

圖2 射頻自我偏壓產生機制示意圖

然而離子通過電漿鞘層到達晶圓表面的過程是需要時間的(τi),且遠大於射頻功率週期時間(τrf ),τi 》τrf,也就是表示離子在到達晶圓表面之前,射頻功率已經切換過好幾次的正負半波(±Vrf),而於正半波時期離子獲得較小的電場加速能量(Ei , min),反之,於負半波週期離子則能獲得最大的電場加速能量(Ei , max),因此,對於到達晶圓表面的離子其能量會有個分佈範圍(Ei , min ~ Ei , max),如圖3所示利用射頻偏壓吸引離子將產生雙尖峰寬離子能量分佈[6-7]。

圖3 到達晶圓表面之離子能量,受射頻偏壓正負擺盪影響造成雙尖峰寬分佈

更完整的內容歡迎訂購 2022年10月號 (單篇費用:參考材化所定價)

主推方案

無限下載/年 5000元

NT$5,000元

訂閱送出